公司拥有多款低开销、可重构以及高性能后量子密码算法与算子IP核产品,支持通用总线接口与RISC-V扩展指令接口形式,符合NIST发布的FIPS 203/204/205标准,支持密码算法验证程序(Cryptographic Algorithm Validation Program,CAVP)测试。

|

算法/特性 |

FIPS203 |

FIPS204 |

FIPS205 |

FIPS203+FIPS204 |

|

低开销 |

√ |

√ |

√ |

√ |

|

可重构 |

√ |

√ |

√ |

√ |

|

高性能 |

√ |

√ |

√ |

√ |

注:

1、上述IP核均支持通用总线接口与RISC-V扩展指令接口交付

2、上述IP核均支持算子级IP与完整算法级IP交付

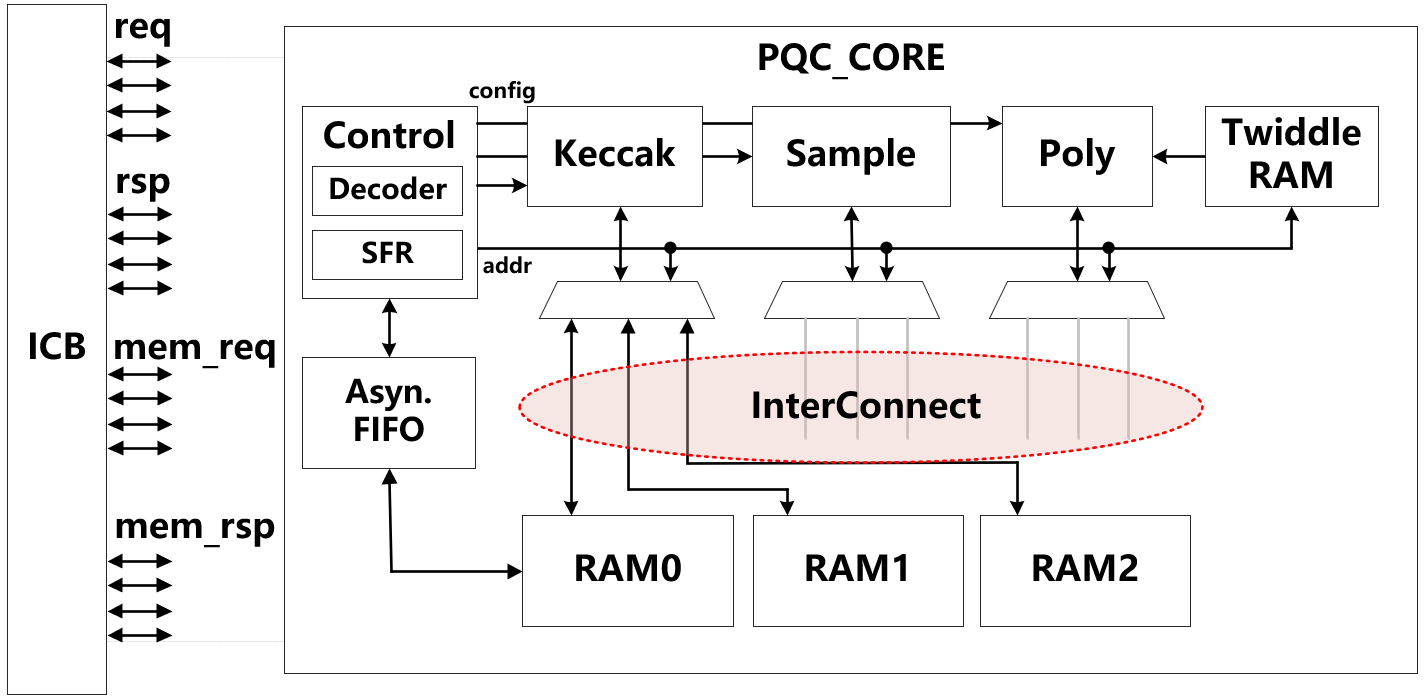

- 可重构算子级PQC IP核:

算子级IP核整体架构包括ICB总线接口、控制(Control)模块、哈希(Keccak)模块、采样(Sample)模块、多项式运算(Poly)模块和存储(RAM)模块。

ICB总线接口用于PQC Core与CPU之间的指令和数据传输,总线包括请求通道(request channel)、响应通道(response channel)、存储请求通道(memory request channel)、存储响应通道(memory response channel)4个通道;

控制模块:用于接收来自CPU发送的扩展指令并进行解码,产生各个核心算子的配置信号、存储器的访存使能与地址信号和特殊功能寄存器读写控制信号;

哈希模块:包括一个Keccak核心电路;

采样模块:包括拒绝采样电路、二项采样电路两部分通用采样电路和可定制采样电路;

多项式运算模块:包括多模运算单元电路;

存储模块:包括SRAM电路。

- 低开销算法级PQC IP核:

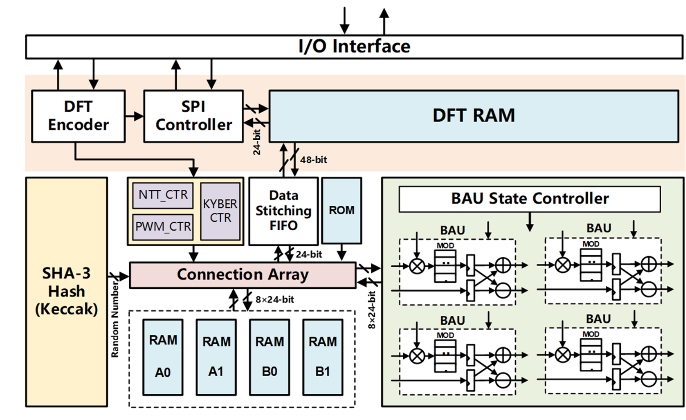

IP核采用高效紧凑型后量子密码Kyber芯片架构,面向分布式边缘计算的轻量化后量子密码Kyber算法实现。该设计利用Keccak的半折叠化技术,大幅降低了SHA-3模块的资源开销及能量消耗。同时,可配置的模运算单元可以灵活调整硬件结构,高效完成不同类型的快速多项式计算。

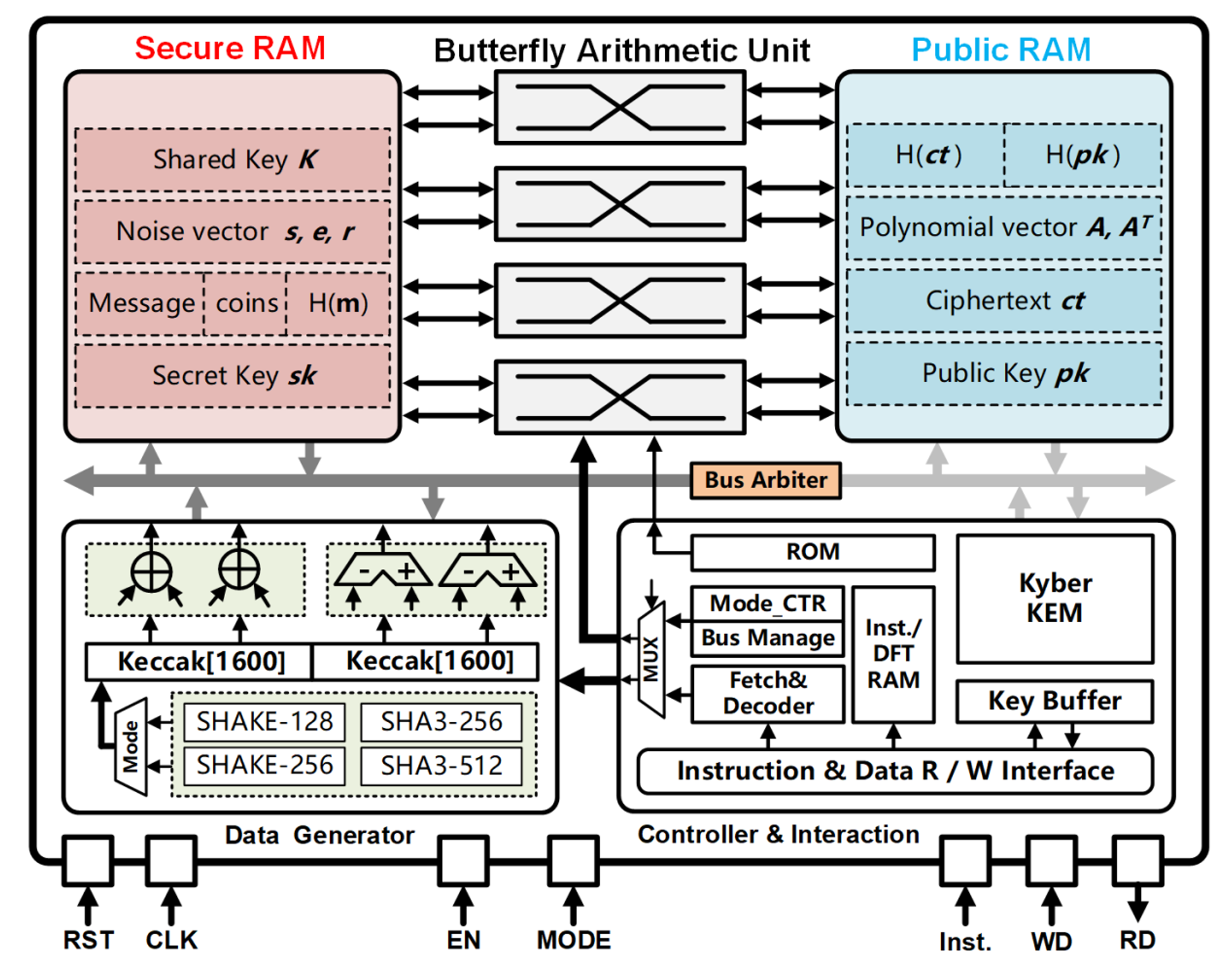

- 可重构FIPS203 PQC算法IP核:

IP核采用核心算子分解算法优化技术,实现了多项式矩阵运算细粒度拆分,同时基于高能效可重构芯片架构,实现了Kyber算法多样化安全参数的高效兼容,支持Kyber国际标准算法全部的Kyber512/768/1024安全等级及完整功能。

- 高性能FIPS203/204/205 PQC算法IP核:

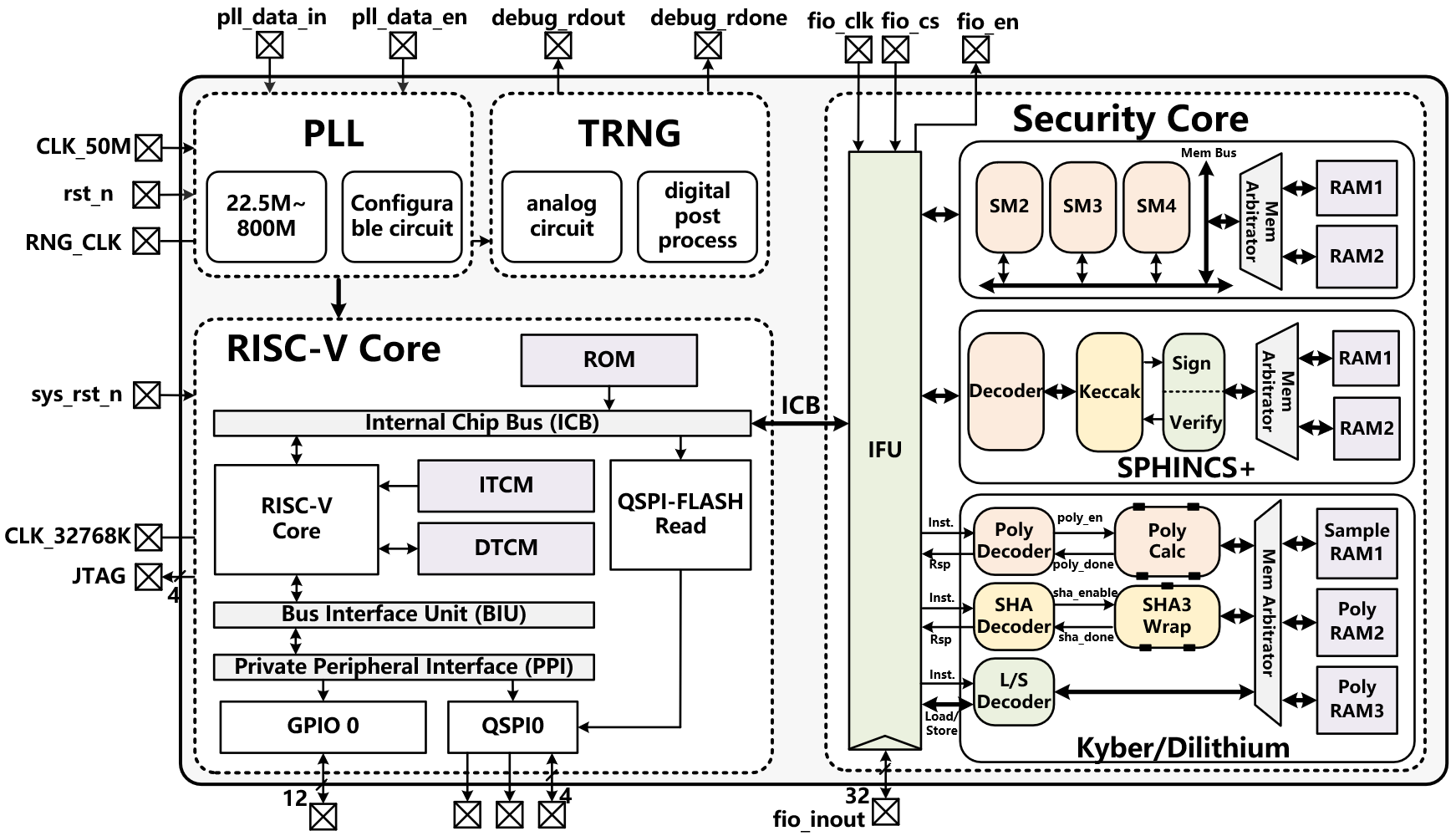

IP核包含PLL、TRNG、RISC-V Core和Security Core,其中PLL负责为整体系统提供高频时钟;TRNG产生真随机数;RISC-V Core负责执行软件代码和程序控制;Security Core为硬件密码协处理器核,负责进行FIPS 203/204/205算法硬件加速。

Security Core内部的SPHINCS+协处理器拥有独立的内部数据存储器RAM,Kyber、Dilithium共用数据存储器RAM,实现加解密、数字签名验签、密钥生成等密码操作所需的数据缓存。RISC-V Core和Security Core之间通过ICB总线进行连接,其中Kyber、Dilithium共用一个ICB接口,SPHINCS+使用一个ICB接口。RISC-V Core根据用户编写的程序,经过编译执行后通过ICB接口控制对应的密码协处理器进行运算加速,运算结果通过异步FIO接口进行输出。

IP核最高工作频率为800MHz,FIPS203算法峰值密钥封装/解封装性能为20万次/秒,FIPS204算法峰值签名/验签性能为6万次/秒,FIPS205算法峰值签名/验签性能为2千次/秒。